Saat meneliti status daya CPU Core 2 ("C-state "), saya benar-benar berhasil mengimplementasikan dukungan untuk sebagian besar prosesor Intel Core/Core 2 lama. Implementasi lengkap (patch Linux) dengan semua informasi latar belakang didokumentasikan di sini.

Ketika saya mengumpulkan lebih banyak informasi tentang prosesor ini, mulai menjadi jelas bahwa C-states yang didukung dalam model Core 2 jauh lebih kompleks daripada prosesor sebelumnya dan yang lebih baru. Ini dikenal sebagai Status-C yang Disempurnakan (atau "CxE "), yang melibatkan paket, inti individu, dan komponen lain pada chipset (mis., memori). Pada saat itu intel_idle driver dirilis, kodenya tidak terlalu matang dan beberapa prosesor Core 2 telah dirilis yang memiliki dukungan C-state yang bertentangan.

Beberapa informasi menarik tentang dukungan Core 2 Solo/Duo C-state ditemukan di artikel ini dari tahun 2006. Hal ini berkaitan dengan dukungan pada Windows, namun ini menunjukkan dukungan perangkat keras C-state yang kuat pada prosesor ini. Informasi mengenai Kentsfield bertentangan dengan nomor model sebenarnya, jadi saya yakin mereka sebenarnya mengacu pada Yorkfield di bawah ini:

... prosesor quad-core Intel Core 2 Extreme (Kentsfield) mendukung kelima teknologi kinerja dan hemat daya — Enhanced IntelSpeedStep (EIST), Thermal Monitor 1 (TM1) dan Thermal Monitor 2 (TM2), Old-Demand Clock Modulation ( ODCM), serta Enhanced C States (CxE). Dibandingkan dengan prosesor Intel Pentium 4 dan Pentium D 600, 800, dan 900, yang ditandai hanya dengan Enhanced Halt (C1) State, fungsi ini telah diperluas pada prosesor Intel Core 2 (serta prosesor Intel Core Solo/Duo) untuk semua kemungkinan status idle prosesor, termasuk Stop Grant (C2), Deep Sleep (C3), dan DeeperSleep (C4).

Artikel dari tahun 2008 ini menguraikan dukungan untuk C-states per-core pada prosesor Intel multi-core, termasuk Core 2 Duo dan Core 2 Quad (bacaan latar belakang tambahan yang membantu ditemukan dalam buku putih dari Dell ini):

C-state inti adalah C-state perangkat keras. Ada beberapa keadaan menganggur inti, mis. CC1 dan CC3. Seperti yang kita ketahui, prosesor canggih modern memiliki banyak inti, seperti prosesor seluler Core DuoT5000/T7000 yang baru dirilis, yang dikenal sebagai Penryn di beberapa kalangan. Apa yang dulu kita anggap sebagai CPU / prosesor, sebenarnya memiliki banyak CPU tujuan umum di dalamnya. Intel Core Duo memiliki 2 inti dalam chip prosesor. Intel Core-2 Quad memiliki 4 inti seperti chip perprosesor. Masing-masing core ini memiliki status diam sendiri. Ini masuk akal karena satu inti mungkin menganggur sementara yang lain bekerja keras pada utas. Jadi C-state inti adalah status diam dari salah satu core tersebut.

Saya menemukan presentasi tahun 2010 dari Intel yang memberikan latar belakang tambahan tentang intel_idle driver, tapi sayangnya tidak menjelaskan kurangnya dukungan untuk Core 2:

Driver PERCOBAAN ini menggantikan acpi_idle pada Prosesor Intel Atom, Prosesor Intel Core i3/i5/i7 dan Prosesor Intel Xeon terkait. Itu tidak mendukung prosesor Intel Core2 atau yang lebih lama.

Presentasi di atas menunjukkan bahwa intel_idle driver adalah implementasi dari pengatur CPU "menu", yang berdampak pada konfigurasi kernel Linux (mis., CONFIG_CPU_IDLE_GOV_LADDER vs. CONFIG_CPU_IDLE_GOV_MENU ). Perbedaan antara tangga dan pengatur menu dijelaskan secara ringkas dalam jawaban ini.

Dell memiliki artikel bermanfaat yang mencantumkan kompatibilitas C-state C0 hingga C6:

Mode C1 ke C3 pada dasarnya bekerja dengan memotong sinyal jam yang digunakan di dalam CPU, sedangkan mode C4 ke C6 bekerja dengan mengurangi voltase CPU. Mode "Ditingkatkan" dapat melakukan keduanya sekaligus.

Mode Name CPUs

C0 Operating State All CPUs

C1 Halt 486DX4 and above

C1E Enhanced Halt All socket LGA775 CPUs

C1E — Turion 64, 65-nm Athlon X2 and Phenom CPUs

C2 Stop Grant 486DX4 and above

C2 Stop Clock Only 486DX4, Pentium, Pentium MMX, K5, K6, K6-2, K6-III

C2E Extended Stop Grant Core 2 Duo and above (Intel only)

C3 Sleep Pentium II, Athlon and above, but not on Core 2 Duo E4000 and E6000

C3 Deep Sleep Pentium II and above, but not on Core 2 Duo E4000 and E6000; Turion 64

C3 AltVID AMD Turion 64

C4 Deeper Sleep Pentium M and above, but not on Core 2 Duo E4000 and E6000 series; AMD Turion 64

C4E/C5 Enhanced Deeper Sleep Core Solo, Core Duo and 45-nm mobile Core 2 Duo only

C6 Deep Power Down 45-nm mobile Core 2 Duo only

Dari tabel ini (yang kemudian saya temukan salah dalam beberapa kasus), tampak bahwa ada berbagai perbedaan dukungan C-state dengan prosesor Core 2 (Perhatikan bahwa hampir semua prosesor Core 2 adalah Socket LGA775, kecuali Core 2 Solo SU3500, yang merupakan prosesor Socket BGA956 dan Merom/Penryn. Prosesor "Intel Core" Solo/Duo adalah salah satu dari Socket PBGA479 atau PPGA478).

Pengecualian tambahan untuk tabel ditemukan di artikel ini:

Intel Core 2 Duo E8500 mendukung C-states C2 dan C4, sedangkan Core 2Extreme QX9650 tidak.

Menariknya, QX9650 adalah prosesor Yorkfield (keluarga Intel 6, model 23, stepping 6). Sebagai referensi, Q9550S saya adalah keluarga Intel 6, model 23 (0x17), melangkah 10, yang seharusnya mendukung C-state C4 (dikonfirmasi melalui eksperimen). Selain itu, Core 2 Solo U3500 memiliki CPUID (family, model, stepping) yang identik dengan Q9550S tetapi tersedia dalam soket non-LGA775, yang mengacaukan interpretasi tabel di atas.

Jelas, CPUID harus digunakan setidaknya hingga langkah demi langkah untuk mengidentifikasi dukungan C-state untuk model prosesor ini, dan dalam beberapa kasus mungkin tidak mencukupi (belum ditentukan saat ini).

Tanda tangan metode untuk menetapkan informasi idle CPU adalah:

#define ICPU(model, cpu) \

{ X86_VENDOR_INTEL, 6, model, X86_FEATURE_ANY, (unsigned long)&cpu }

Dimana model disebutkan dalam asm/intel-family.h. Saat memeriksa file header ini, saya melihat bahwa CPU Intel diberi pengenal 8-bit yang tampaknya cocok dengan nomor model keluarga Intel 6:

#define INTEL_FAM6_CORE2_PENRYN 0x17

Dari penjelasan di atas, kami memiliki Intel Family 6, Model 23 (0x17) yang didefinisikan sebagai INTEL_FAM6_CORE2_PENRYN . Ini seharusnya cukup untuk menentukan status tidak aktif untuk sebagian besar prosesor Model 23, tetapi berpotensi menyebabkan masalah dengan QX9650 seperti disebutkan di atas.

Jadi, minimal, setiap grup prosesor yang memiliki kumpulan C-state yang berbeda perlu ditentukan dalam daftar ini.

Zagacki dan Ponnala, Jurnal Teknologi Intel 12 (3):219-227, 2008 menunjukkan bahwa prosesor Yorkfield memang mendukung C2 dan C4. Mereka juga tampaknya menunjukkan bahwa spesifikasi ACPI 3.0a hanya mendukung transisi antara C-states C0, C1, C2 dan C3, yang saya duga juga dapat membatasi acpi_idle Linux driver untuk transisi antara set C-states yang terbatas itu. Namun, artikel ini menunjukkan bahwa mungkin tidak selalu demikian:

Ingatlah bahwa ini adalah status ACPI C, bukan prosesor, jadi ACPIC3 mungkin HW C6, dll.

Juga perlu diperhatikan:

Di luar prosesor itu sendiri, karena C4 merupakan upaya sinkronisasi antara komponen silikon utama dalam platform, Chipset Intel Q45 Express mencapai peningkatan daya sebesar 28 persen.

Chipset yang saya gunakan memang Chipset Intel Q45 Express.

Dokumentasi Intel tentang status MWAIT singkat tetapi menegaskan perilaku ACPI khusus BIOS:

C-states khusus prosesor yang ditentukan dalam ekstensi MWAIT dapat dipetakan ke tipe C-state yang ditentukan ACPI (C0, C1, C2, C3). Hubungan pemetaan bergantung pada definisi C-state oleh implementasi prosesor dan diekspos ke OSPM oleh BIOS menggunakan tabel _CST yang ditentukan ACPI.

Interpretasi saya atas tabel di atas (dikombinasikan dengan tabel dari Wikipedia, asm/intel-family.h dan artikel di atas) adalah:

Model 9 0x09 (Pentium M dan Celeron M ):

- Banias:C0, C1, C2, C3, C4

Model 13 0x0D (Pentium M dan Celeron M ):

- Dothan, Stealey:C0, C1, C2, C3, C4

Model 14 0x0E INTEL_FAM6_CORE_YONAH (Pentium M yang Disempurnakan , Celeron M yang Disempurnakan atau Intel Core ):

- Yonah (Inti Solo , Core Duo ):C0, C1, C2, C3, C4, C4E/C5

Model 15 0x0F INTEL_FAM6_CORE2_MEROM (beberapa Core 2 dan Pentium Dual-Core ):

- Kentsfield, Merom, Conroe, Allendale (E2xxx/E4xxx dan Core 2 Duo E6xxx, T7xxxx/T8xxxx , Core 2 Extreme QX6xxx , Core 2 Quad Q6xxx ):C0, C1, C1E, C2, C2E

Model 23 0x17 INTEL_FAM6_CORE2_PENRYN (Inti 2 ):

- Merom-L/Penryn-L:?

- Penryn (Core 2 Duo 45-nm seluler ):C0, C1, C1E, C2, C2E, C3, C4, C4E/C5, C6

- Yorkfield (Core 2 Extreme QX9650 ):C0, C1, C1E, C2E?, C3

- Wolfdale/Yorkfield (Core 2 Quad , C2Q Xeon , Core 2 Duo E5xxx/E7xxx/E8xxx , Pentium Dual-Core E6xxx , Celeron Dual-Core ):C0, C1, C1E, C2, C2E, C3, C4

Dari jumlah keragaman dalam dukungan C-state hanya dalam jajaran prosesor Core 2, tampaknya kurangnya dukungan yang konsisten untuk C-states mungkin menjadi alasan untuk tidak berusaha mendukung mereka sepenuhnya melalui intel_idle pengemudi. Saya ingin melengkapi daftar di atas untuk seluruh baris Core 2.

Ini sebenarnya bukan jawaban yang memuaskan, karena membuat saya bertanya-tanya berapa banyak daya yang tidak perlu digunakan dan kelebihan panas yang telah (dan masih) dihasilkan dengan tidak sepenuhnya memanfaatkan status-C MWAIT hemat daya yang kuat pada prosesor ini.

Chattopadhyay dkk. 2018, Prosesor Kinerja Tinggi Hemat Energi:Pendekatan Terbaru untuk Merancang Komputasi Kinerja Tinggi Ramah Lingkungan patut diperhatikan untuk perilaku spesifik yang saya cari di Q45 Express Chipset:

Paket C-state (PC0-PC10) - Saat domain komputasi, Core dan Grafik (GPU) tidak digunakan, prosesor memiliki peluang untuk penghematan daya tambahan pada level uncore dan platform, misalnya, membilas LLC dan memperkuat pengontrol memori dan DRAM IO, dan pada keadaan tertentu, seluruh prosesor dapat dimatikan sementara keadaannya dipertahankan pada domain daya yang selalu aktif.

Sebagai ujian, saya memasukkan baris berikut di linux/drivers/idle/intel_idle.c 127:

static struct cpuidle_state conroe_cstates[] = {

{

.name = "C1",

.desc = "MWAIT 0x00",

.flags = MWAIT2flg(0x00),

.exit_latency = 3,

.target_residency = 6,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C1E",

.desc = "MWAIT 0x01",

.flags = MWAIT2flg(0x01),

.exit_latency = 10,

.target_residency = 20,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

// {

// .name = "C2",

// .desc = "MWAIT 0x10",

// .flags = MWAIT2flg(0x10),

// .exit_latency = 20,

// .target_residency = 40,

// .enter = &intel_idle,

// .enter_s2idle = intel_idle_s2idle, },

{

.name = "C2E",

.desc = "MWAIT 0x11",

.flags = MWAIT2flg(0x11),

.exit_latency = 40,

.target_residency = 100,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.enter = NULL }

};

static struct cpuidle_state core2_cstates[] = {

{

.name = "C1",

.desc = "MWAIT 0x00",

.flags = MWAIT2flg(0x00),

.exit_latency = 3,

.target_residency = 6,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C1E",

.desc = "MWAIT 0x01",

.flags = MWAIT2flg(0x01),

.exit_latency = 10,

.target_residency = 20,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C2",

.desc = "MWAIT 0x10",

.flags = MWAIT2flg(0x10),

.exit_latency = 20,

.target_residency = 40,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C2E",

.desc = "MWAIT 0x11",

.flags = MWAIT2flg(0x11),

.exit_latency = 40,

.target_residency = 100,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C3",

.desc = "MWAIT 0x20",

.flags = MWAIT2flg(0x20) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 85,

.target_residency = 200,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C4",

.desc = "MWAIT 0x30",

.flags = MWAIT2flg(0x30) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 100,

.target_residency = 400,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C4E",

.desc = "MWAIT 0x31",

.flags = MWAIT2flg(0x31) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 100,

.target_residency = 400,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.name = "C6",

.desc = "MWAIT 0x40",

.flags = MWAIT2flg(0x40) | CPUIDLE_FLAG_TLB_FLUSHED,

.exit_latency = 200,

.target_residency = 800,

.enter = &intel_idle,

.enter_s2idle = intel_idle_s2idle, },

{

.enter = NULL }

};

di intel_idle.c baris 983:

static const struct idle_cpu idle_cpu_conroe = {

.state_table = conroe_cstates,

.disable_promotion_to_c1e = false,

};

static const struct idle_cpu idle_cpu_core2 = {

.state_table = core2_cstates,

.disable_promotion_to_c1e = false,

};

di intel_idle.c baris 1073:

ICPU(INTEL_FAM6_CORE2_MEROM, idle_cpu_conroe),

ICPU(INTEL_FAM6_CORE2_PENRYN, idle_cpu_core2),

Setelah kompilasi cepat dan reboot node PXE saya, dmesg sekarang menunjukkan:

[ 0.019845] cpuidle: using governor menu

[ 0.515785] clocksource: acpi_pm: mask: 0xffffff max_cycles: 0xffffff, max_idle_ns: 2085701024 ns

[ 0.543404] intel_idle: MWAIT substates: 0x22220

[ 0.543405] intel_idle: v0.4.1 model 0x17

[ 0.543413] tsc: Marking TSC unstable due to TSC halts in idle states deeper than C2

[ 0.543680] intel_idle: lapic_timer_reliable_states 0x2

Dan sekarang PowerTOP menunjukkan:

Package | CPU 0

POLL 2.5% | POLL 0.0% 0.0 ms

C1E 2.9% | C1E 5.0% 22.4 ms

C2 0.4% | C2 0.2% 0.2 ms

C3 2.1% | C3 1.9% 0.5 ms

C4E 89.9% | C4E 92.6% 66.5 ms

| CPU 1

| POLL 10.0% 400.8 ms

| C1E 5.1% 6.4 ms

| C2 0.3% 0.1 ms

| C3 1.4% 0.6 ms

| C4E 76.8% 73.6 ms

| CPU 2

| POLL 0.0% 0.2 ms

| C1E 1.1% 3.7 ms

| C2 0.2% 0.2 ms

| C3 3.9% 1.3 ms

| C4E 93.1% 26.4 ms

| CPU 3

| POLL 0.0% 0.7 ms

| C1E 0.3% 0.3 ms

| C2 1.1% 0.4 ms

| C3 1.1% 0.5 ms

| C4E 97.0% 45.2 ms

Saya akhirnya mengakses Enhanced Core 2 C-states, dan sepertinya ada penurunan konsumsi daya yang dapat diukur - meteran saya pada 8 node tampaknya rata-rata setidaknya 5% lebih rendah (dengan satu node masih menjalankan kernel lama) , tetapi saya akan mencoba menukar kernel lagi sebagai percobaan.

Catatan menarik tentang dukungan C4E - Prosesor Yorktown Q9550S saya tampaknya mendukungnya (atau sub-status C4 lainnya), sebagaimana dibuktikan di atas! Ini membingungkan saya, karena lembar data Intel pada prosesor Core 2 Q9000 (bagian 6.2) hanya menyebutkan C-states Normal (C0), HALT (C1 =0x00), Extended HALT (C1E =0x01), Stop Grant (C2 =0x10) , Hibah Berhenti Diperpanjang (C2E =0x11), Tidur/Tidur Nyenyak (C3 =0x20) dan Tidur Lebih Dalam (C4 =0x30). Apa status tambahan 0x31 ini? Jika saya mengaktifkan status C2, maka C4E digunakan sebagai pengganti C4. Jika saya menonaktifkan keadaan C2 (memaksa keadaan C2E) maka C4 digunakan sebagai pengganti C4E. Saya menduga ini mungkin ada hubungannya dengan bendera MWAIT, tetapi saya belum menemukan dokumentasi untuk perilaku ini.

Saya tidak yakin apa yang membuat ini:Status C1E tampaknya digunakan sebagai pengganti C1, C2 digunakan sebagai pengganti C2E dan C4E digunakan sebagai pengganti C4. Saya tidak yakin apakah C1/C1E, C2/C2E dan C4/C4E dapat digunakan bersama dengan intel_idle atau jika mereka berlebihan. Saya menemukan catatan dalam presentasi tahun 2010 ini oleh Intel Labs Pittsburgh yang menunjukkan transisinya adalah C0 - C1 - C0 - C1E - C0, dan selanjutnya menyatakan:

C1E hanya digunakan saat semua core berada di C1E

Saya percaya itu harus ditafsirkan sebagai status C1E dimasukkan pada komponen lain (mis. Memori) hanya ketika semua inti berada dalam status C1E. Saya juga mengambil ini untuk diterapkan secara setara ke negara bagian C2/C2E dan C4/C4E (Meskipun C4E disebut sebagai "C4E/C5" jadi saya tidak yakin apakah C4E adalah sub-status C4 atau jika C5 adalah sub- keadaan C4E. Pengujian sepertinya menunjukkan C4/C4E sudah benar). Saya dapat memaksa C2E untuk digunakan dengan mengomentari status C2 - namun, ini menyebabkan status C4 digunakan alih-alih C4E (lebih banyak pekerjaan mungkin diperlukan di sini). Semoga tidak ada prosesor model 15 atau model 23 yang tidak memiliki status C2E, karena prosesor tersebut akan terbatas pada C1/C1E dengan kode di atas.

Selain itu, nilai bendera, latensi, dan tempat tinggal mungkin dapat disetel dengan baik, tetapi hanya mengambil tebakan berdasarkan nilai menganggur Nehalem tampaknya berfungsi dengan baik. Diperlukan lebih banyak bacaan untuk melakukan perbaikan.

Saya mengujinya pada Core 2 Duo E2220 (Allendale), Dual Core Pentium E5300 (Wolfdale), Core 2 Duo E7400, Core 2 Duo E8400 (Wolfdale), Core 2 Quad Q9550S (Yorkfield) dan Core 2 Extreme QX9650, dan saya tidak menemukan masalah selain preferensi yang disebutkan sebelumnya untuk status C2/C2E dan C4/C4E.

Tidak dicakup oleh modifikasi driver ini:

- Core Solo/Core Duo asli (Yonah, non Core 2) adalah keluarga 6, model 14. Ini bagus karena mereka mendukung C-states C4E/C5 (Enhanced Deep Sleep) tetapi bukan C1E/C2E dan akan membutuhkan definisi menganggur mereka sendiri.

Satu-satunya masalah yang dapat saya pikirkan adalah:

- Core 2 Solo SU3300/SU3500 (Penryn-L) adalah keluarga 6, model 23 dan akan terdeteksi oleh driver ini. Namun, mereka bukan Socket LGA775 sehingga mereka mungkin tidak mendukung C1E Enhanced Halt C-state. Begitu juga dengan Core 2 Solo ULV U2100/U2200 (Merom-L). Namun,

intel_idledriver tampaknya memilih C1/C1E yang sesuai berdasarkan dukungan perangkat keras dari sub-negara bagian. - Core 2 Extreme QX9650 (Yorkfield) dilaporkan tidak mendukung C-state C2 atau C4. Saya telah mengonfirmasi hal ini dengan membeli prosesor Optiplex 780 dan QX9650 Extreme bekas di eBay. Prosesor mendukung C-states C1 dan C1E. Dengan modifikasi driver ini, CPU idle dalam status C1E, bukan C1, sehingga mungkin ada penghematan daya. Saya berharap melihat C-state C3, tetapi tidak ada saat menggunakan driver ini, jadi saya mungkin perlu memeriksanya lebih jauh.

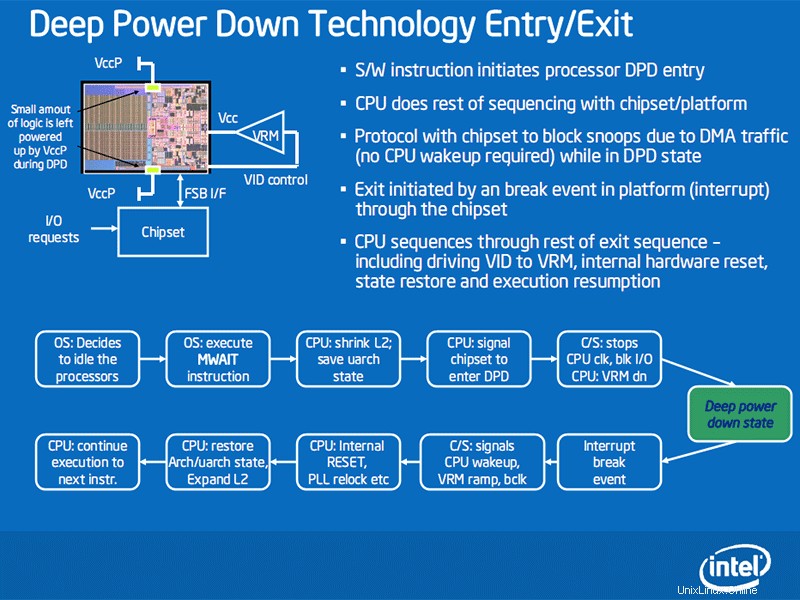

Saya berhasil menemukan slide dari presentasi Intel tahun 2009 tentang transisi antara C-states (yaitu, Deep Power Down):

Kesimpulannya, ternyata tidak ada alasan sebenarnya untuk kurangnya dukungan Core 2 di intel_idle pengemudi. Jelas sekarang bahwa kode rintisan asli untuk "Core 2 Duo" hanya menangani C-states C1 dan C2, yang akan jauh lebih efisien daripada acpi_idle fungsi yang juga menangani C-state C3. Setelah saya tahu ke mana harus mencari, mengimplementasikan dukungan menjadi mudah. Komentar yang bermanfaat dan jawaban lainnya sangat kami hargai, dan jika Amazon mendengarkan, Anda tahu ke mana harus mengirim cek.

Pembaruan ini telah dilakukan ke github. Saya akan segera mengirimkan email tambalan ke LKML.

Perbarui :Saya juga berhasil menggali Socket T/LGA775 Allendale (Conroe) Core 2 Duo E2220, yaitu keluarga 6, model 15, jadi saya menambahkan dukungan untuk itu juga. Model ini tidak mendukung C-state C4, tetapi mendukung C1/C1E dan C2/C2E. Ini juga harus berfungsi untuk chip berbasis Conroe lainnya (E4xxx/E6xxx) dan mungkin semua prosesor Kentsfield dan Merom (non Merom-L).

Perbarui :Saya akhirnya menemukan beberapa sumber penyetelan MWAIT. Langganan Kekuatan vs. Kinerja ini dan status Deeper C ini serta postingan blog latensi yang meningkat keduanya berisi beberapa informasi berguna untuk mengidentifikasi latensi idle CPU. Sayangnya, ini hanya melaporkan latensi keluar yang dikodekan ke dalam kernel (namun, yang menarik, hanya status perangkat keras yang didukung oleh prosesor):

# cd /sys/devices/system/cpu/cpu0/cpuidle

# for state in `ls -d state*` ; do echo c-$state `cat $state/name` `cat $state/latency` ; done

c-state0/ POLL 0

c-state1/ C1 3

c-state2/ C1E 10

c-state3/ C2 20

c-state4/ C2E 40

c-state5/ C3 20

c-state6/ C4 60

c-state7/ C4E 100

Perbarui: Seorang karyawan Intel baru-baru ini menerbitkan artikel tentang intel_idle merinci status MWAIT.

Apakah ada cara yang lebih tepat untuk mengonfigurasi kernel untuk dukungan idle CPU yang optimal untuk rangkaian prosesor ini (selain menonaktifkan dukungan untuk intel_idle)

Anda telah mengaktifkan ACPI, dan Anda telah memeriksa apakah acpi_idle sedang digunakan. Saya sangat ragu Anda melewatkan opsi konfigurasi kernel yang membantu. Anda selalu dapat memeriksa powertop untuk kemungkinan saran, tetapi mungkin Anda sudah mengetahuinya.

Ini bukan jawaban, tapi saya ingin memformatnya :-(.

Melihat kode sumber kernel, driver intel_idle saat ini berisi pengujian untuk secara khusus mengecualikan keluarga Intel 6 dari driver.

Tidak, tidak :-).

id = x86_match_cpu(intel_idle_ids);

if (!id) {

if (boot_cpu_data.x86_vendor == X86_VENDOR_INTEL &&

boot_cpu_data.x86 == 6)

pr_debug(PREFIX "does not run on family %d model %d\n",

boot_cpu_data.x86, boot_cpu_data.x86_model);

return -ENODEV;

}

if pernyataan tidak mengecualikan Family 6. Sebagai gantinya, if pernyataan memberikan pesan saat debug diaktifkan, bahwa CPU Intel modern khusus ini tidak didukung oleh intel_idle . Faktanya, CPU i5-5300U saya saat ini adalah Family 6 dan menggunakan intel_idle .

Apa yang mengecualikan CPU Anda adalah tidak ada kecocokan di intel_idle_ids meja.

Saya perhatikan komit ini yang mengimplementasikan tabel. Kode yang dihapus memiliki switch pernyataan sebagai gantinya. Hal ini memudahkan untuk melihat bahwa model paling awal intel_idle telah diterapkan/berhasil diuji/berapapun 0x1A =26. https://github.com/torvalds/linux/commit/b66b8b9a4a79087dde1b358a016e5c8739ccf186

Saya menduga ini hanya kasus peluang dan biaya. Ketika intel_idle ditambahkan, tampaknya dukungan Core 2 Duo telah direncanakan, tetapi tidak pernah sepenuhnya diimplementasikan — mungkin pada saat para insinyur Intel menyelesaikannya, itu tidak layak lagi. Persamaannya relatif kompleks:intel_idle perlu memberikan manfaat yang memadai dibandingkan acpi_idle untuk membuatnya layak didukung di sini, pada CPU yang akan melihat kernel yang "ditingkatkan" dalam jumlah yang cukup...

Seperti yang dikatakan oleh jawaban sourcejedi, pengemudi tidak mengecualikan semua keluarga 6. intel_idle pemeriksaan inisialisasi untuk CPU dalam daftar model CPU, yang pada dasarnya mencakup semua arsitektur mikro dari Nehalem hingga Kaby Lake. Yorkfield lebih tua dari itu (dan sangat berbeda - Nehalem sangat berbeda dari arsitektur yang datang sebelumnya). Tes keluarga 6 hanya memengaruhi apakah pesan kesalahan dicetak; efeknya hanya pesan kesalahan hanya akan ditampilkan pada CPU Intel, bukan CPU AMD (keluarga Intel 6 mencakup semua CPU Intel non-NetBurst sejak Pentium Pro).

Untuk menjawab pertanyaan konfigurasi Anda, Anda dapat sepenuhnya menonaktifkan intel_idle , tetapi membiarkannya juga tidak apa-apa (selama Anda tidak keberatan dengan peringatannya).